# New generation EDA tools supporting various MEMS-ASIC integration schemes

Sandeep Akkaraju IntelliSense Corporation

# Outline

- Introduction

- Packaging impact on MEMS

- Challenges in package modeling

- Case studies

- Summary

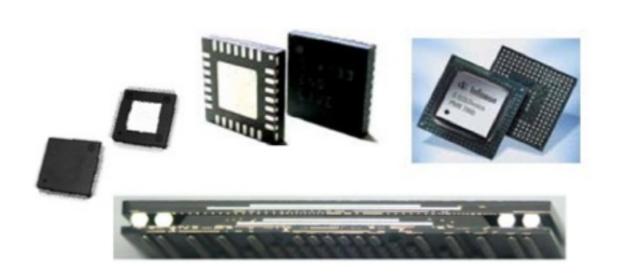

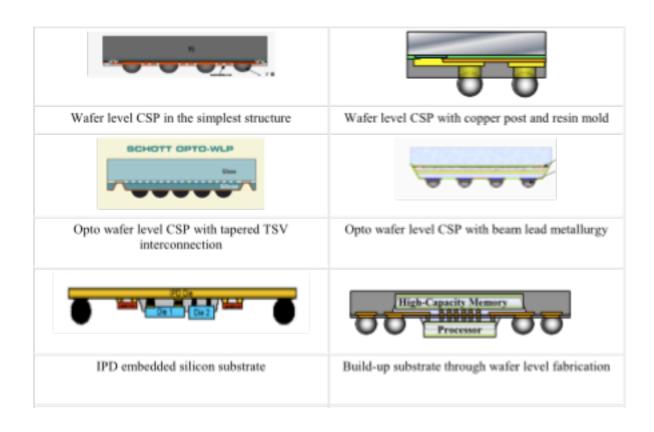

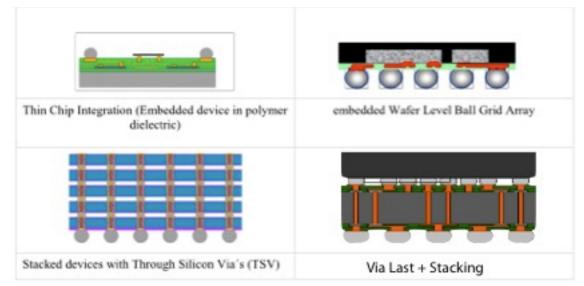

## World of MEMS packaging is evolving rapidly

Learning a new set of TLAs...

**Traditional Packaging**

QFP, QFN, POP, MCM, FBGA ...

Next generation MEMS packaging

3D POP, 3D SIP, 3D WLP, 3D SIC...

#### Minimum Package Volume

## Market drivers...

#### Form factor

Height & footprint (1mm going down to 0.8 mm)

#### Cost

<1 \$ components ⇒ low packaging BOM

#### Integration

GPS + Inertial

BaseBand + Filters

Antennas + Tuners

#### **Environment**

Buzzers & bells, extreme temperatures, mechanical flexing, EM issues

### Reliability

Beyond drop tests: Fatigue, vacuum integrity, hysteresis, product year lifetime issues

# Technology drivers...

#### **Chipscale Packaging**

Stack large number of dies [11 die in 1 mm form factor in 2010 14 die in 0.8 mm in 2014]

#### **Die/Wafer Stacking**

KGD to KGSites

Direct Wafer Stacking

3D Packaging

#### Via Last/Via First/TSV

Match KGD to KG sites at high throughput

#### PoP/eWLP/3DSIC/...

Package on Package Embedded approaches

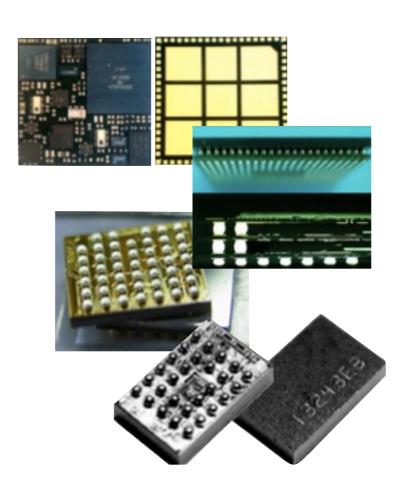

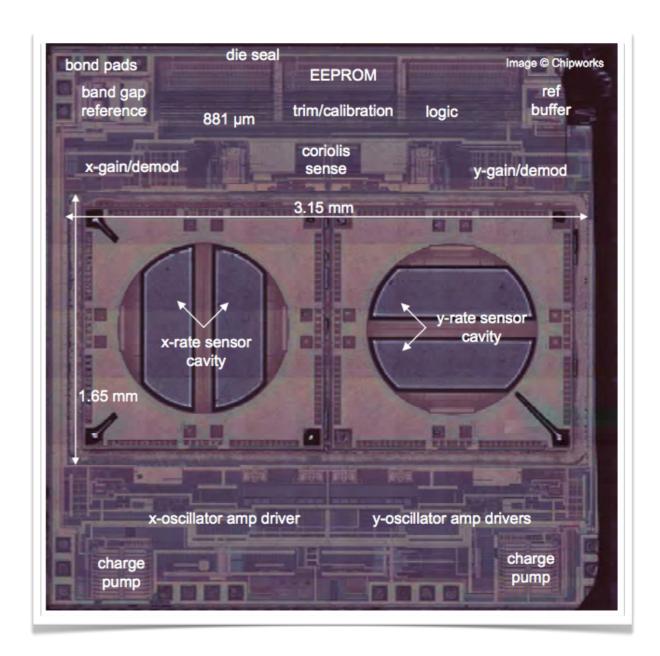

## Invensense gyro: MEMS+ASIC stacking with Al/Ge bonding

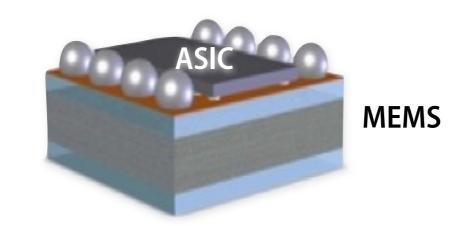

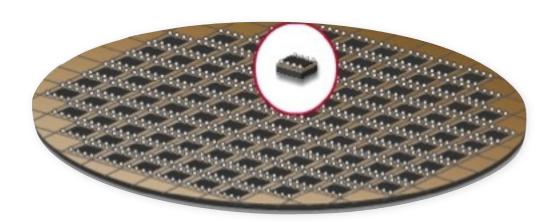

## VTI Accel: Full WLP

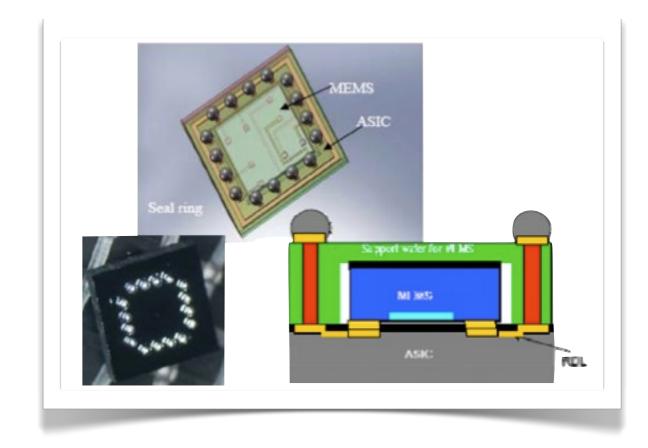

## IME (Singapore)

Die on Wafer Assembly Two level bumping

MEMS ASIC bonding Support Wafer for MEMS with bumps

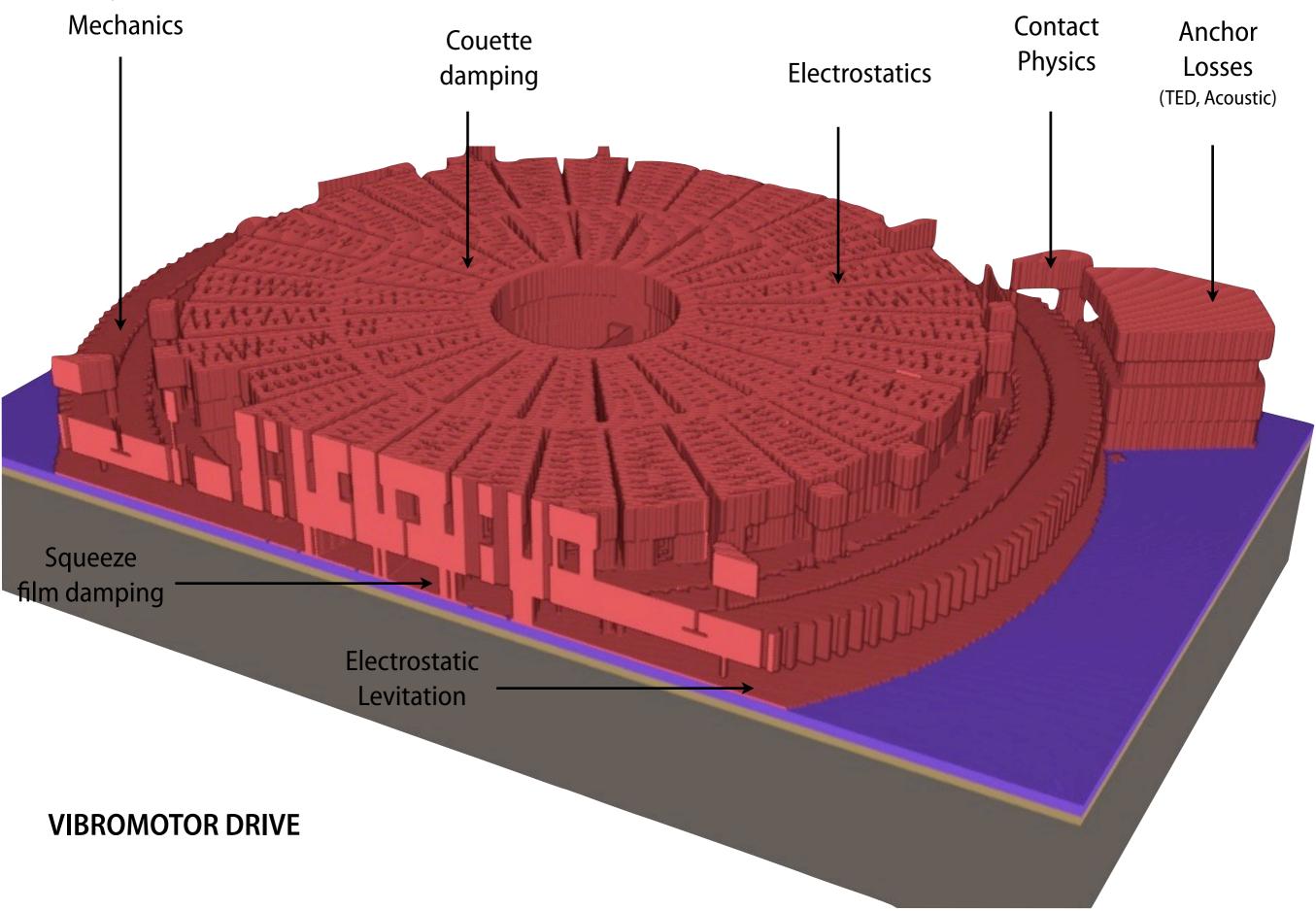

# A typical MEMS device...

| Now, layer pa | ckaging | effects on | top of this. | • • • |

|---------------|---------|------------|--------------|-------|

|---------------|---------|------------|--------------|-------|

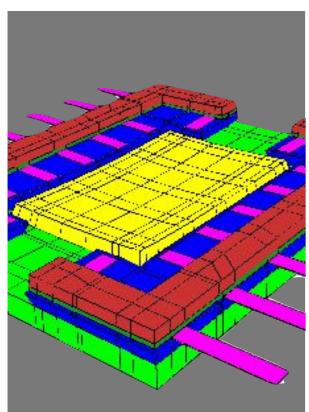

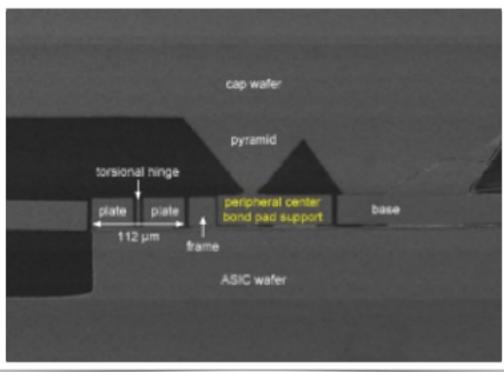

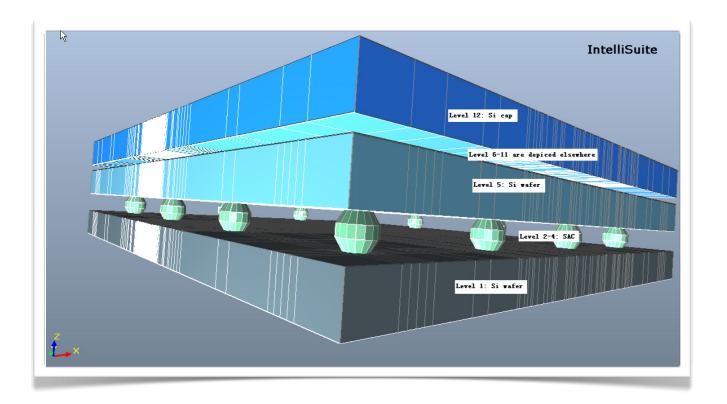

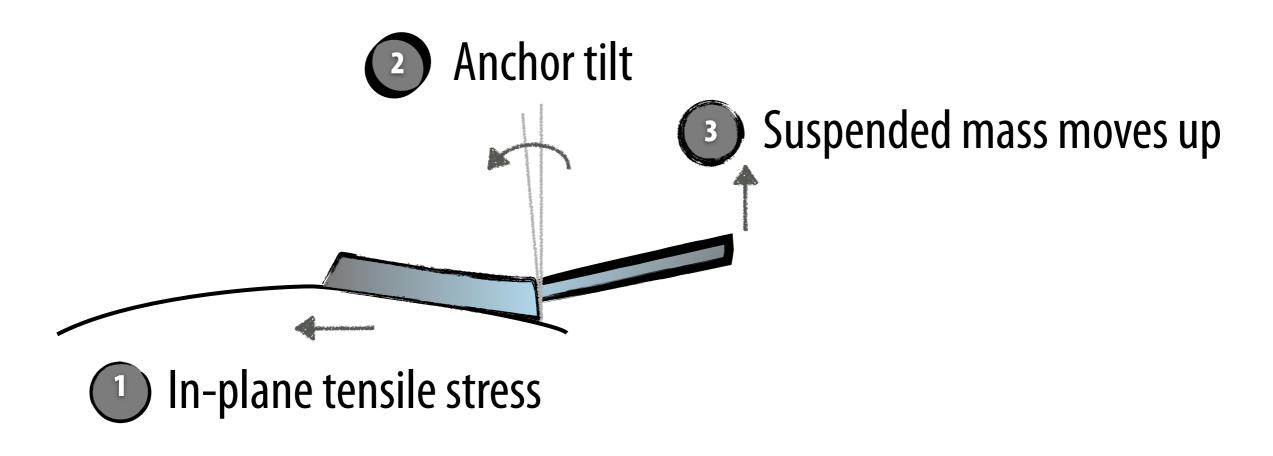

## Thermo-mechanical

#### 3 layer stack:

Cap Wafer

Eutectic Bonded to Device Wafer with TSV

Bumped to ASIC wafer

(underfill not shown)

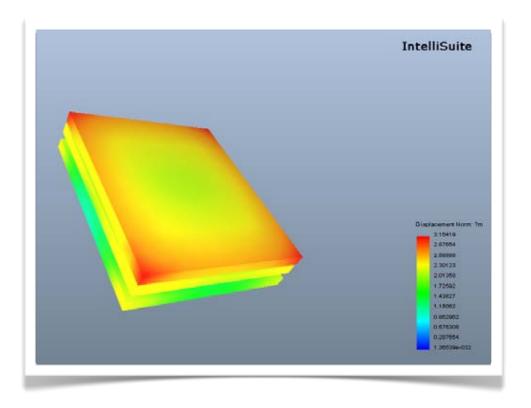

## Thermo-mechanical

## Thermo-mechanical

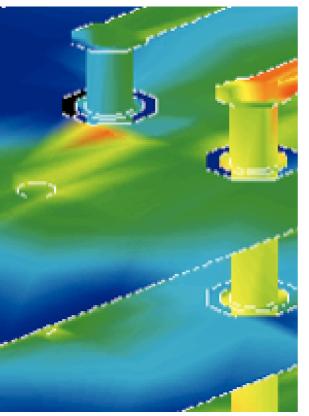

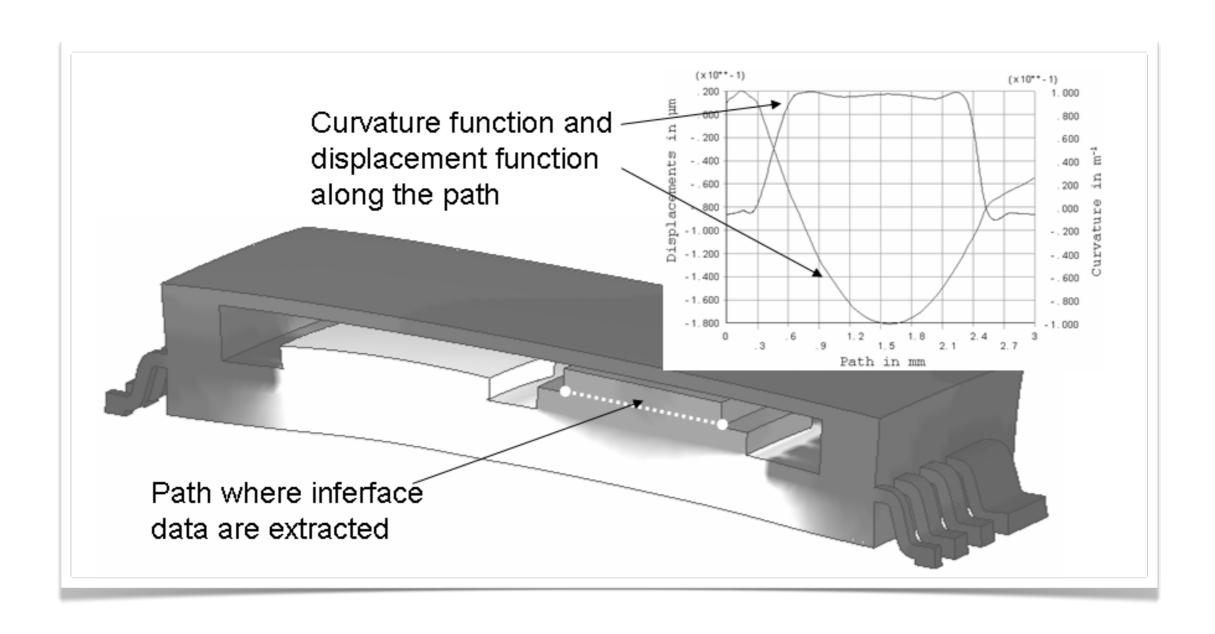

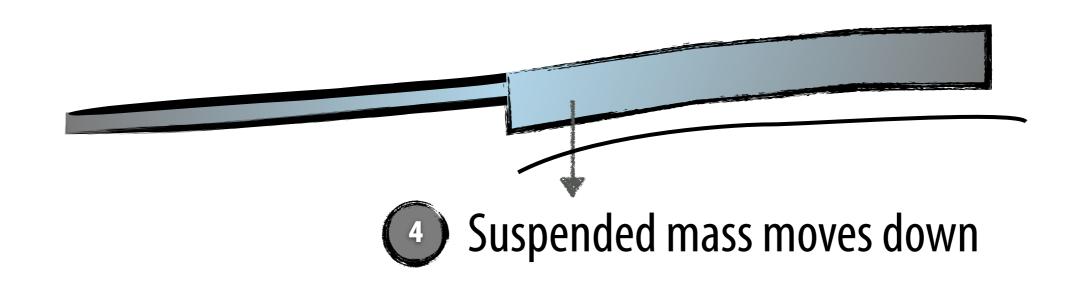

## **Electro-thermal**

Bottom Electrodes

Temperature sensitivity due to curvature

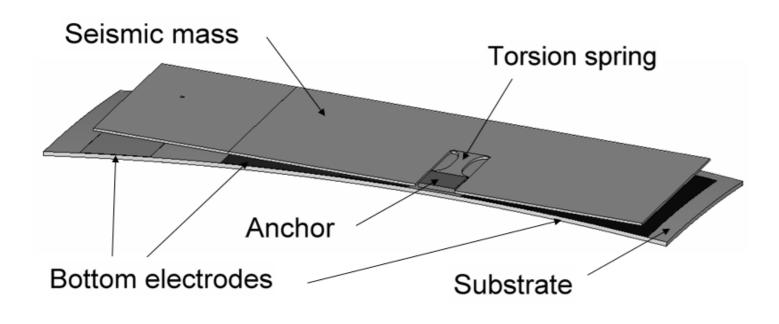

**Comb Electrodes Curvature related sensitivity**

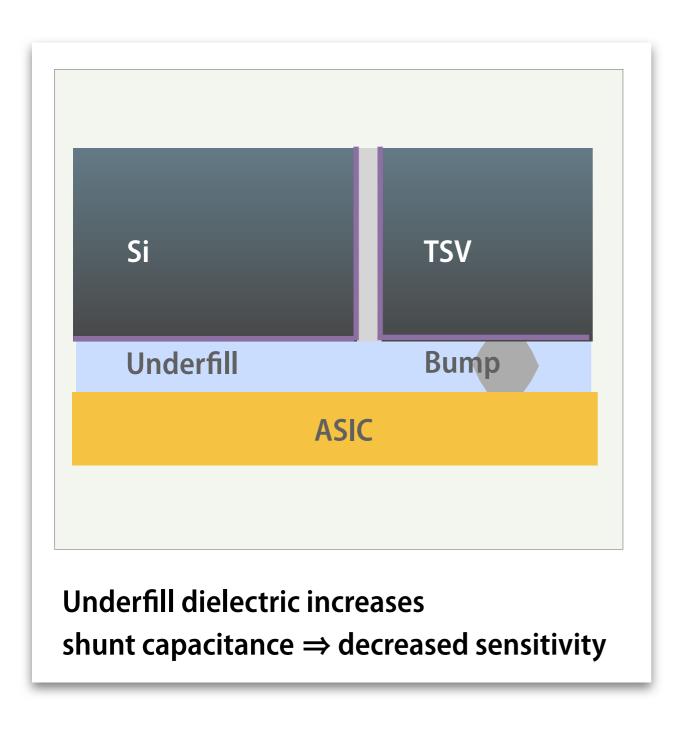

## **Electrical**

Shunt issues

Parasitics & cross talk

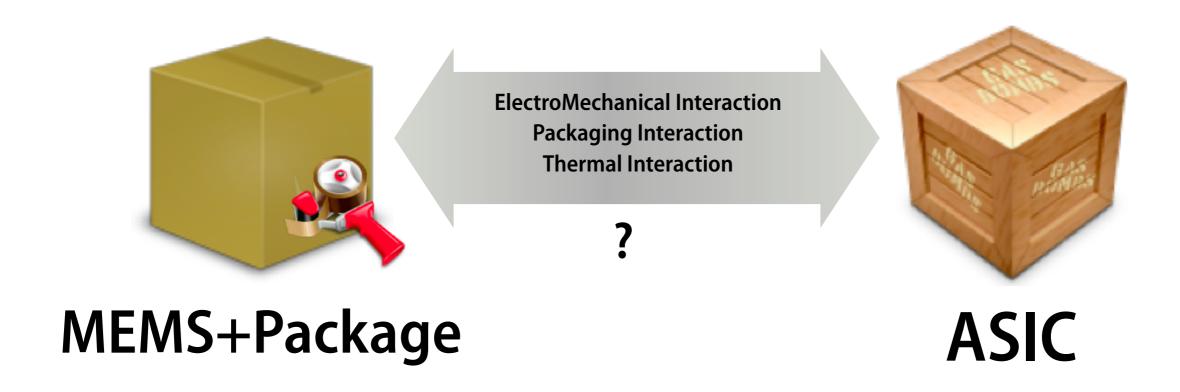

# Packaging impact...

| Mechanical      | Mechanical parameters: stresses, spring constants, damping, shock   |  |

|-----------------|---------------------------------------------------------------------|--|

| Electrical      | Sense & shunt capacitance change; pull-in and tuning voltage change |  |

| Thermal         | Temperature co-efficients, temperature gradient co-efficients       |  |

| Ambient         | Vacuum change, viscosity change in air, moisture effects            |  |

| Electromagnetic | Parasitic capacitances, inductances and resistance                  |  |

Manifests as bias stability, temperature coefficients, and other performance killers...

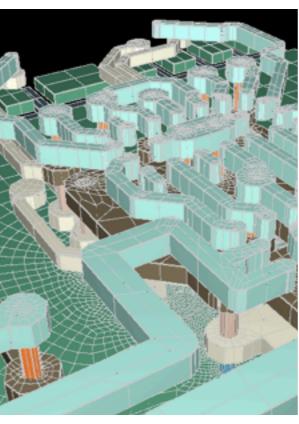

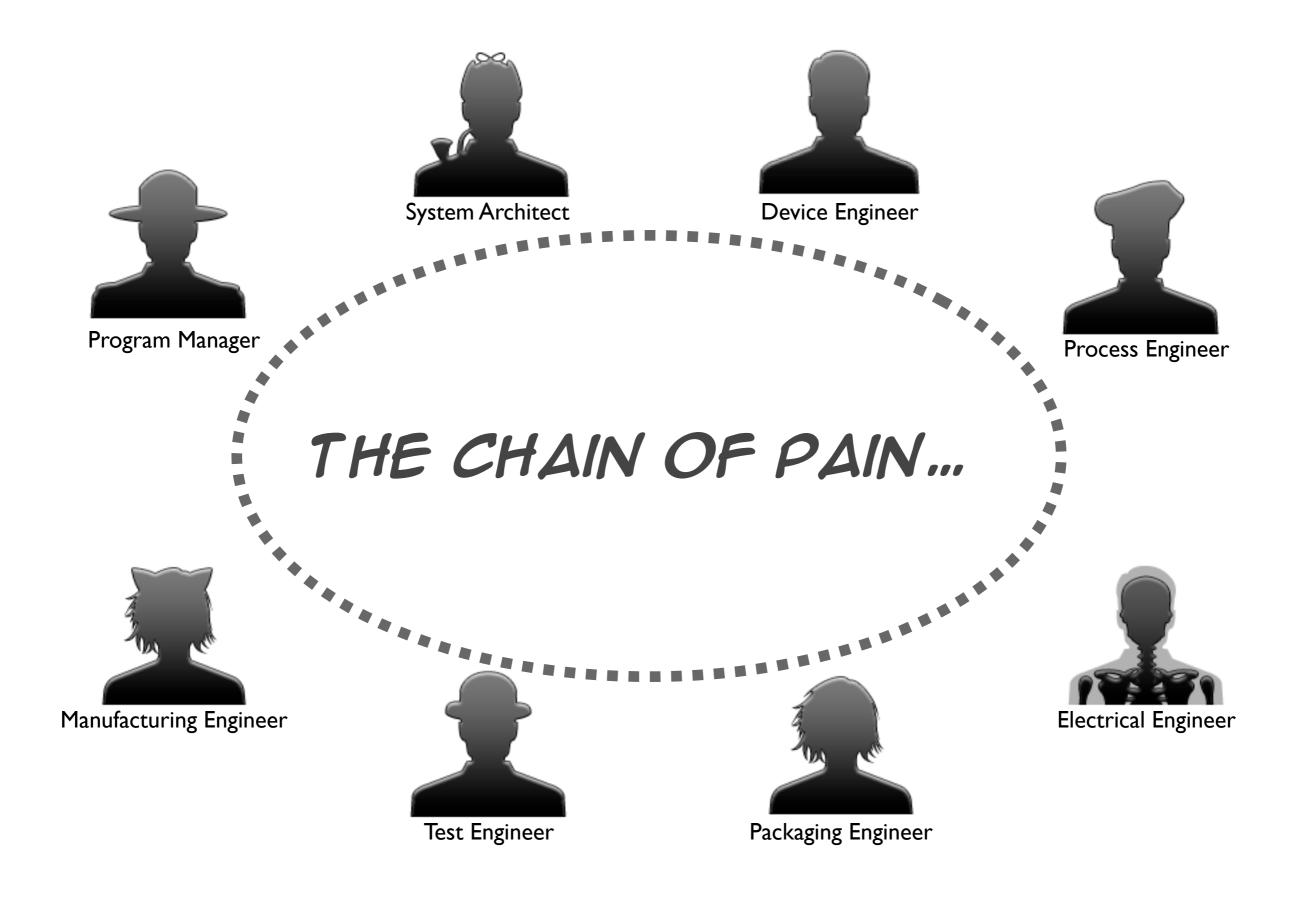

# MEMS Design Is A Collaboration Challenge...

# The chain of pain... (1)

How do you explore a huge range of packaging options?

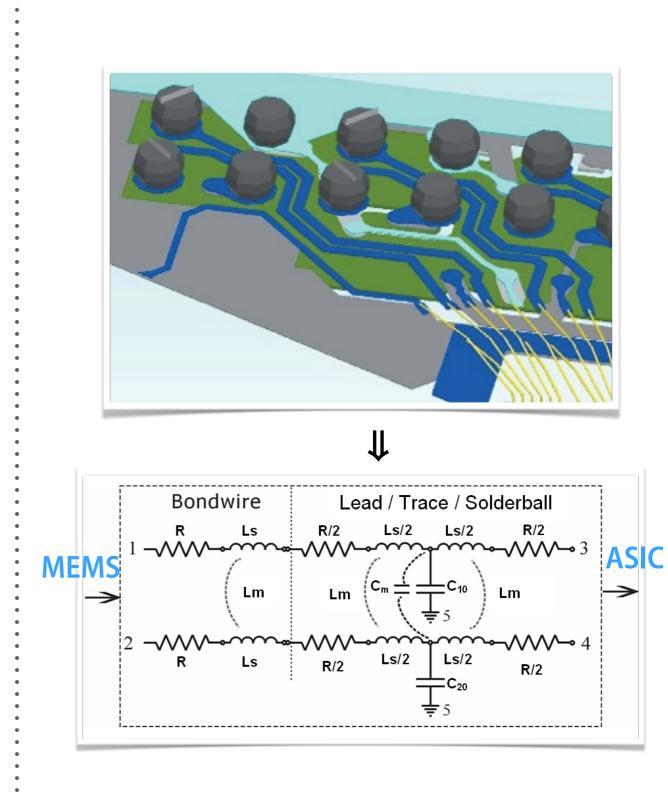

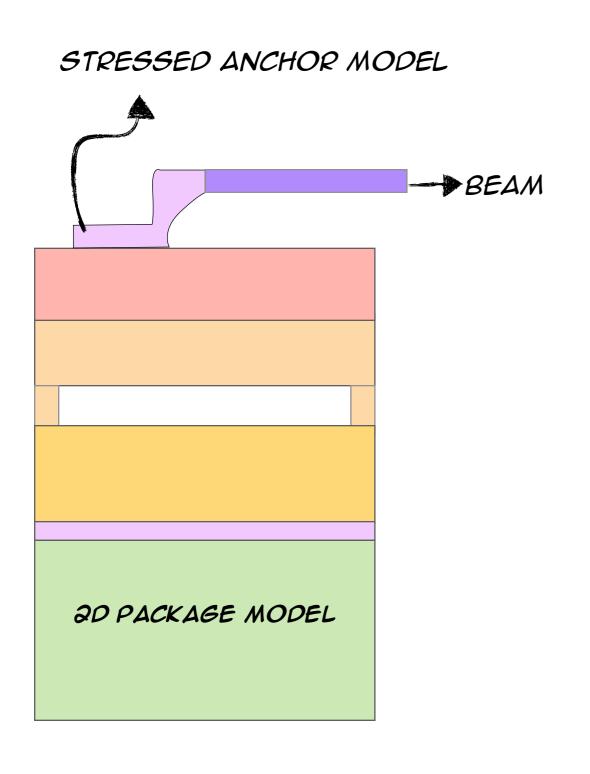

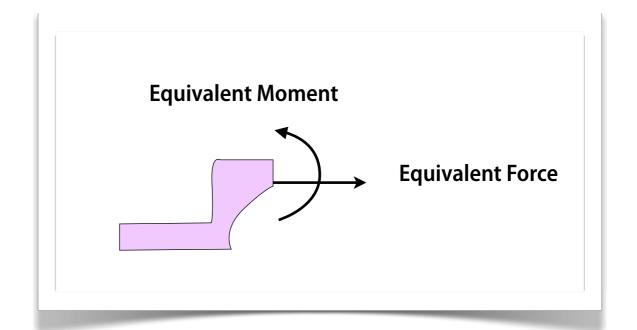

# Compact models for packaging...

# The chain of pain... (2)

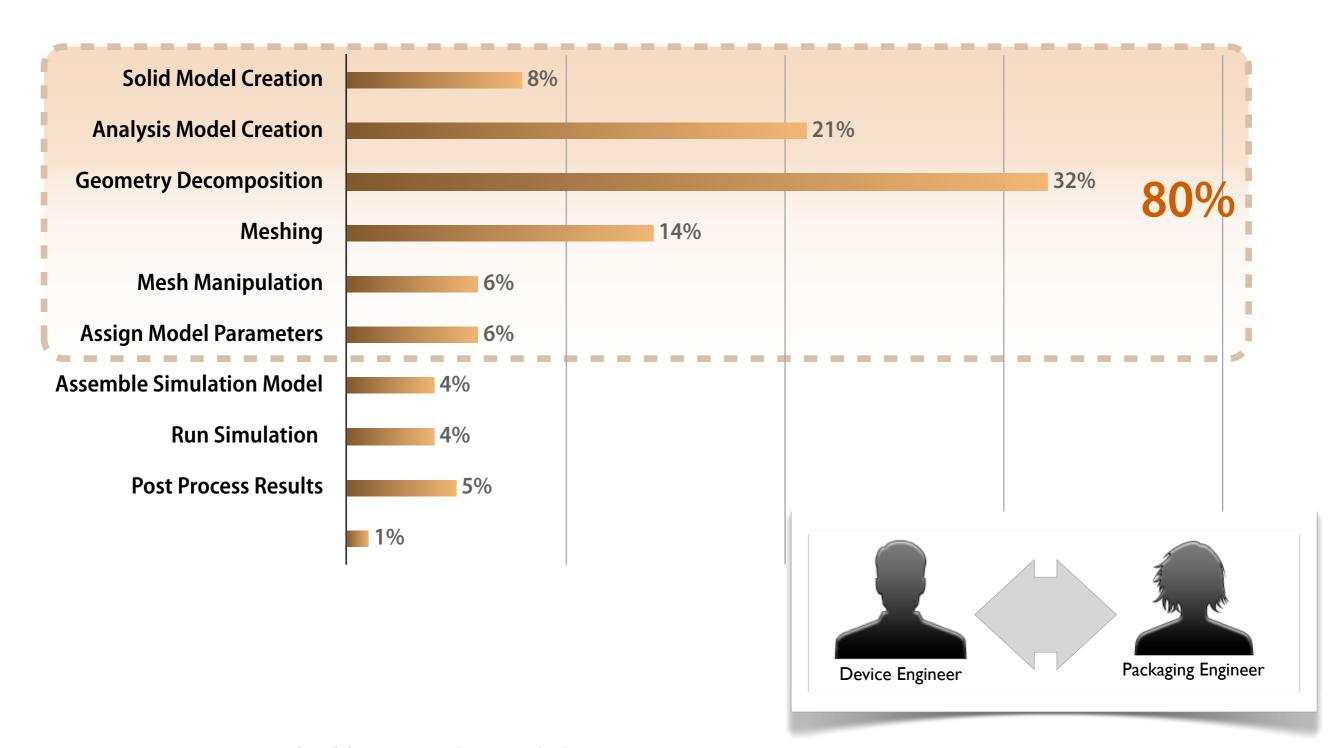

#### How do you efficiently create MEMS + Package models?

Close to 80% of the time spent in mesh creation and manipulation...

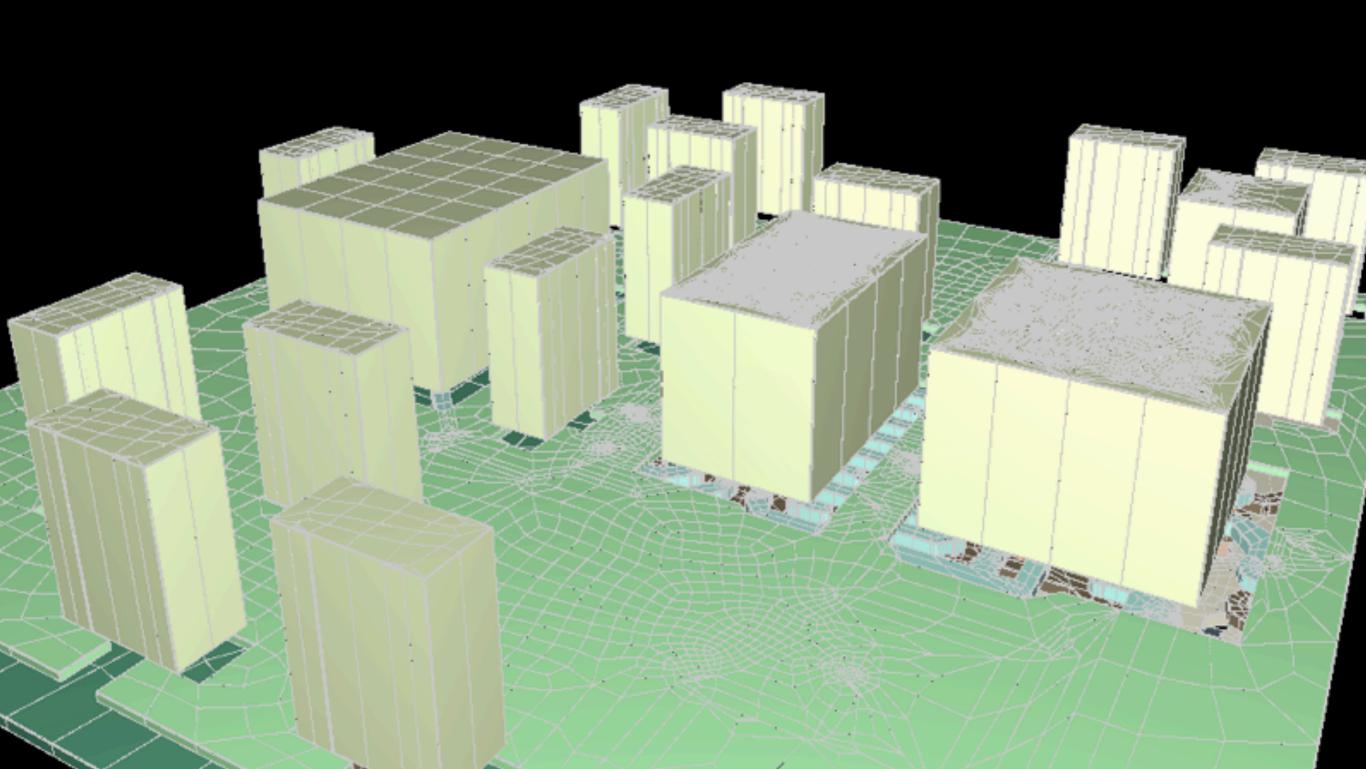

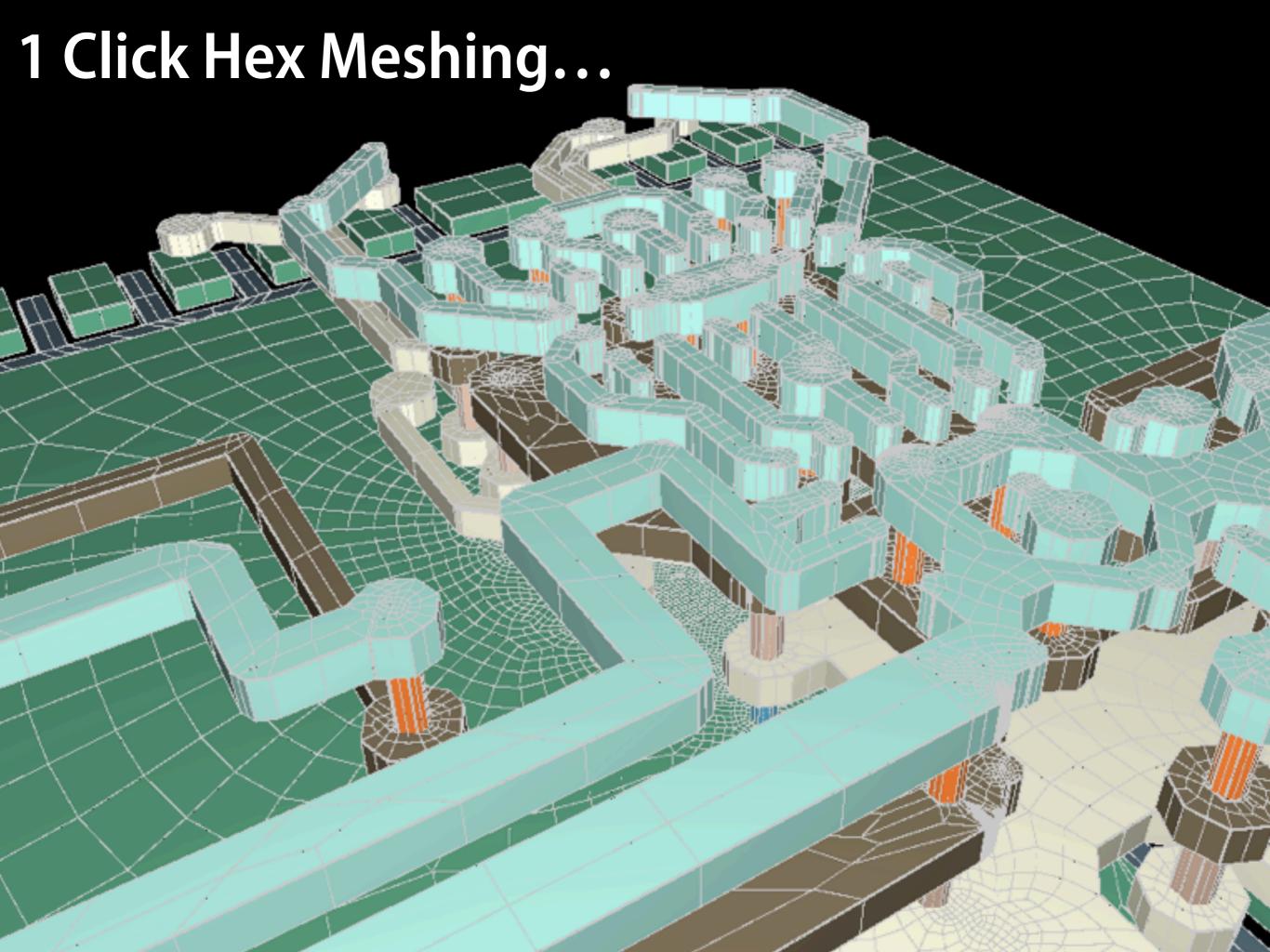

# Automated HEX meshing...

## The chain of pain... (3)

How do you compensate packaging and temperature effects?

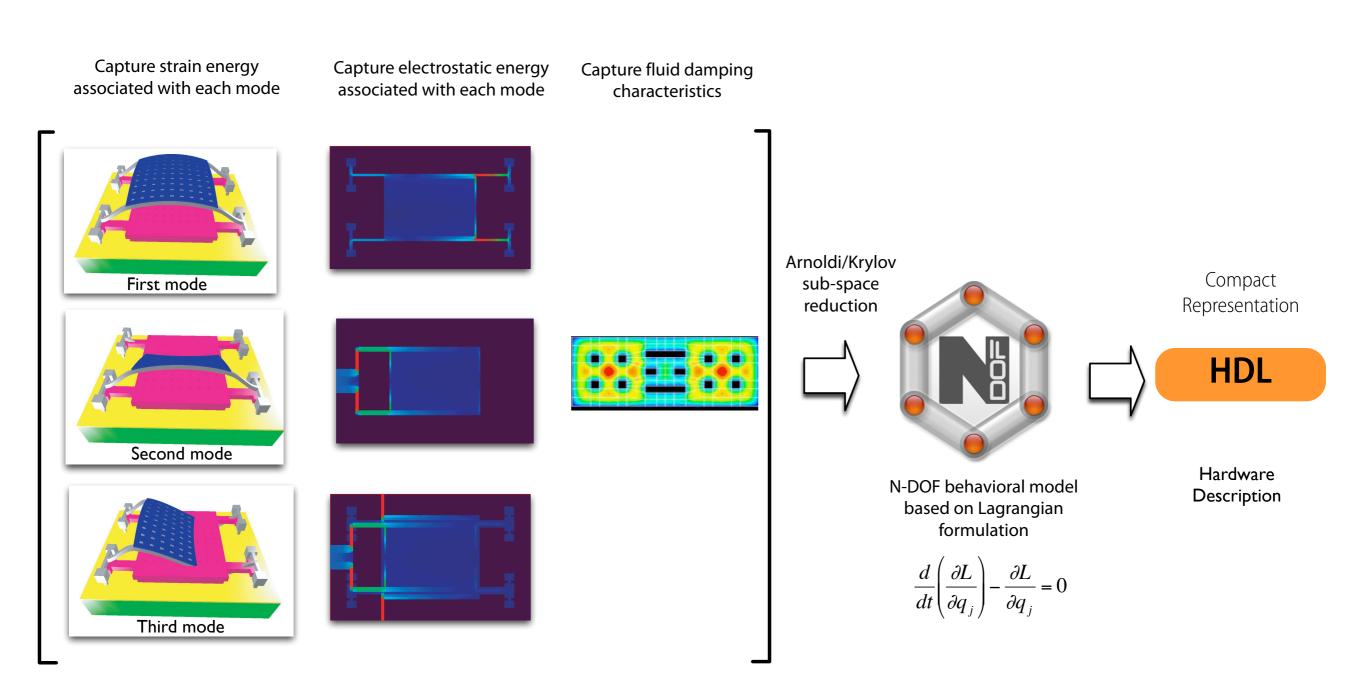

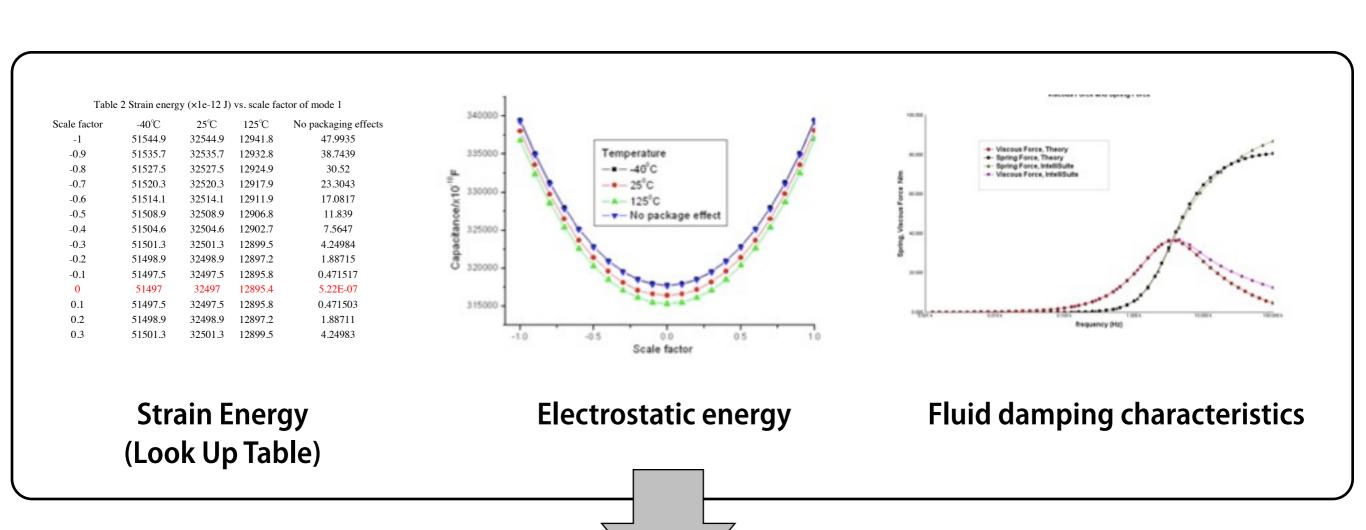

# **Automated System Model Extraction (SME)**

- Capture total energy of relevant mode (Mechanical, Electrostatic, Dissipation)

- Krylov/Arnoldi methods to generate Lagrangian formulation

- Create Compact model for system modeling

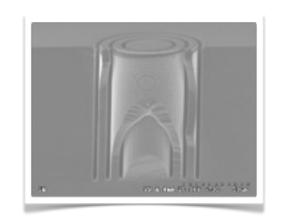

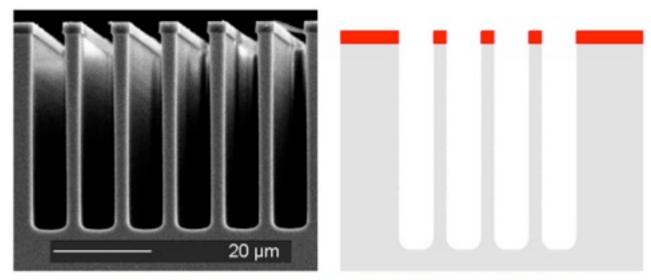

# The chain of pain... (4)

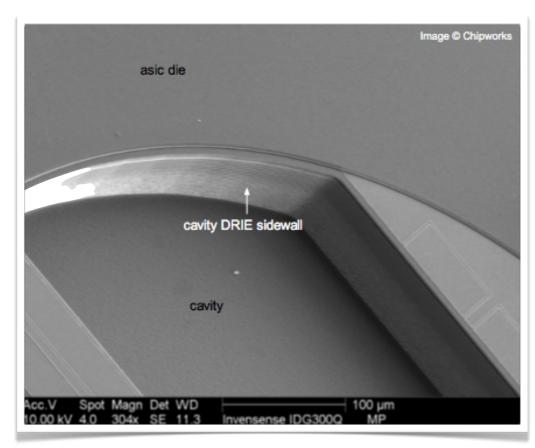

## How do you fine tune TSV processes?

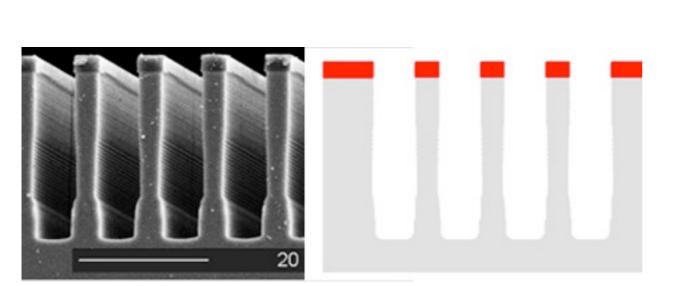

The experimental results of the etching. Comparison of etching 5  $\mu m$  openings with an etch/dep cycle of 7s/7s.

The experimental result of the etching of trenches using three etching steps with different etching/polymerization time configurations. 7s/7s, 9s/7s and 5s/7s are used sequentially, each for 5 minutes.

Comparison of etching a 5  $\mu m$  trench with a 7s/8s cycle

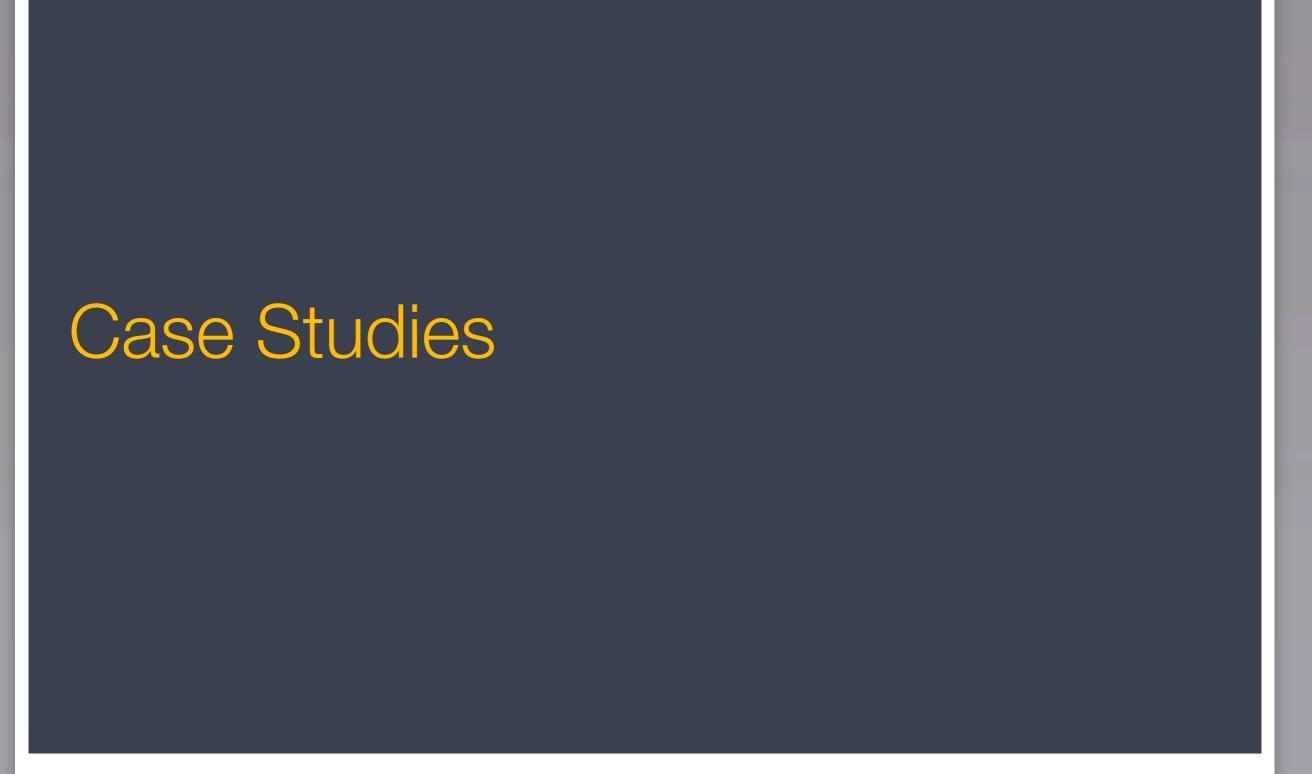

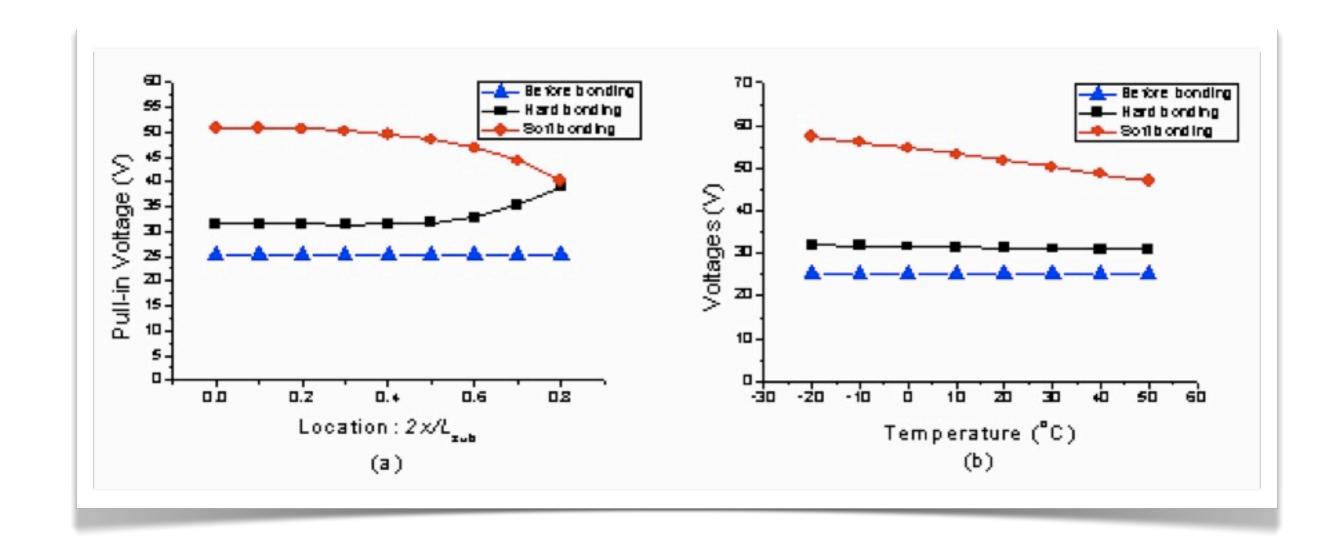

# Northrup: RF Switch

## **RF Switch**

Within 10% of full FEA models...

Hard bonding: Au-Si Eutectic on Ceramic Substrate

**Soft bonding**: Epoxy bonding on FR-4

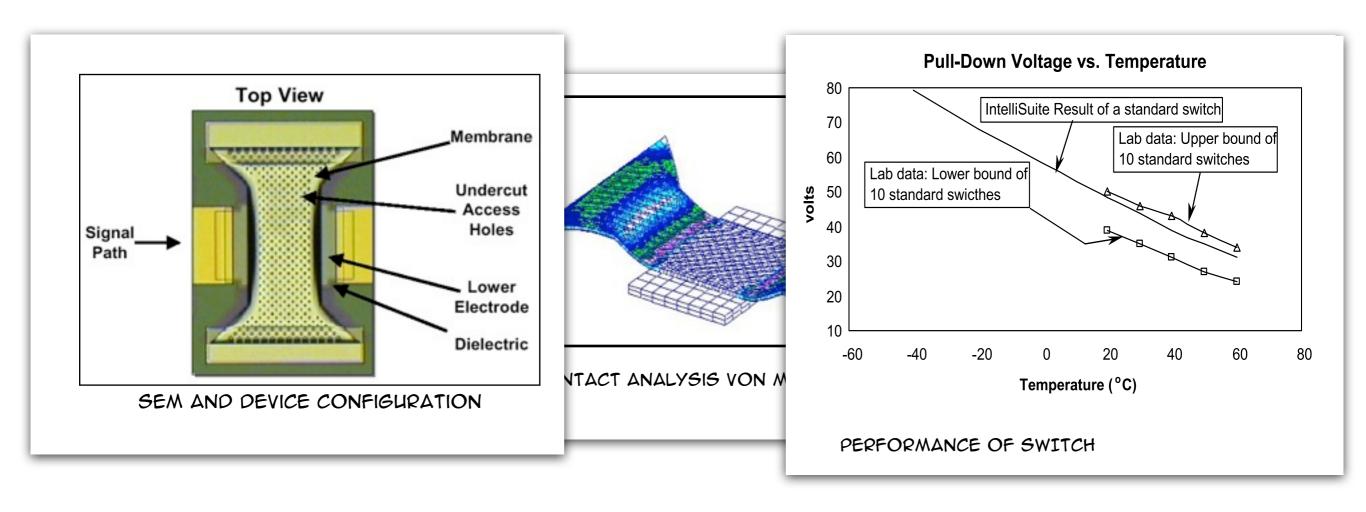

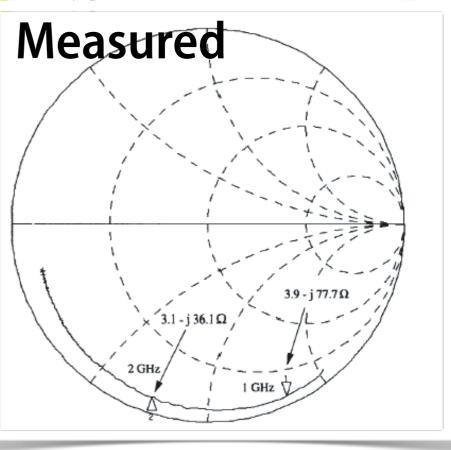

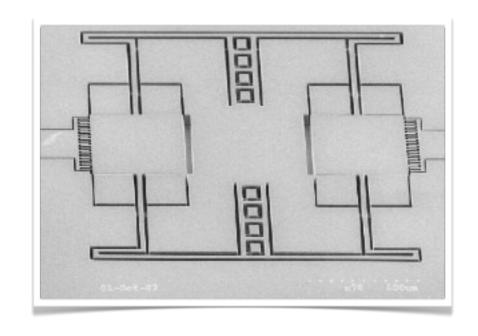

# Raytheon RF Switch

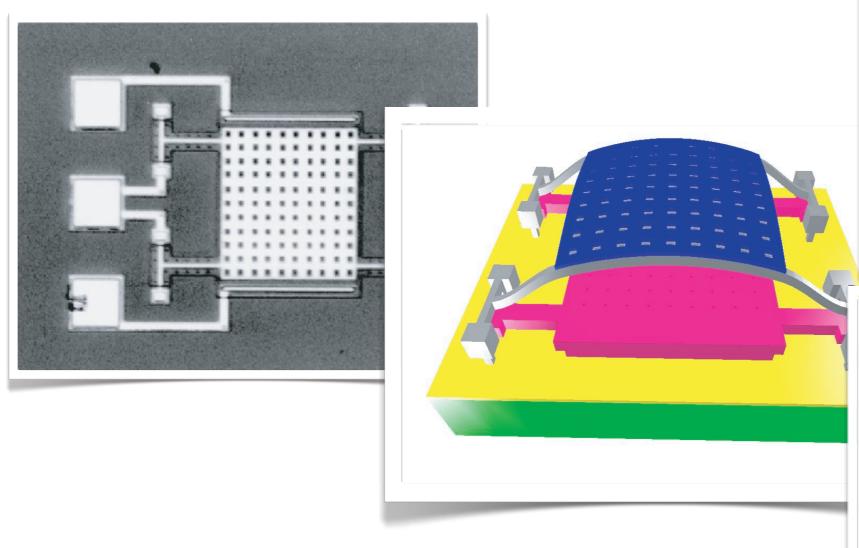

# **Tunable capacitor**

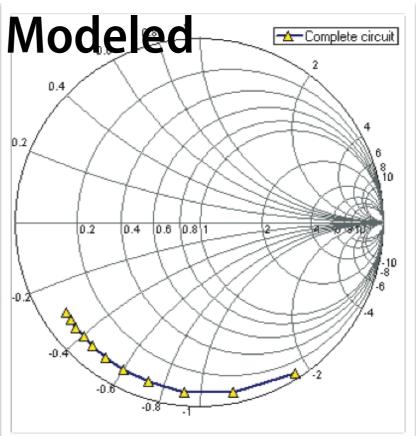

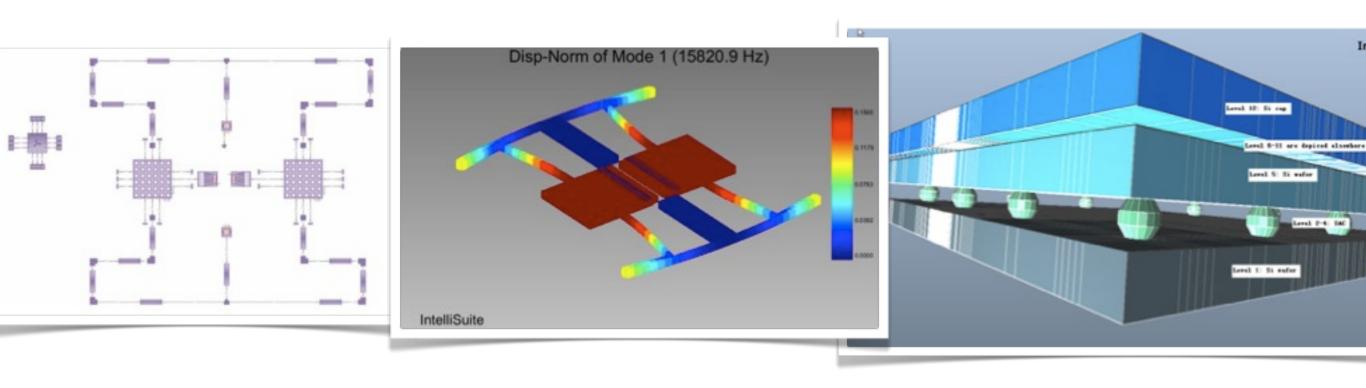

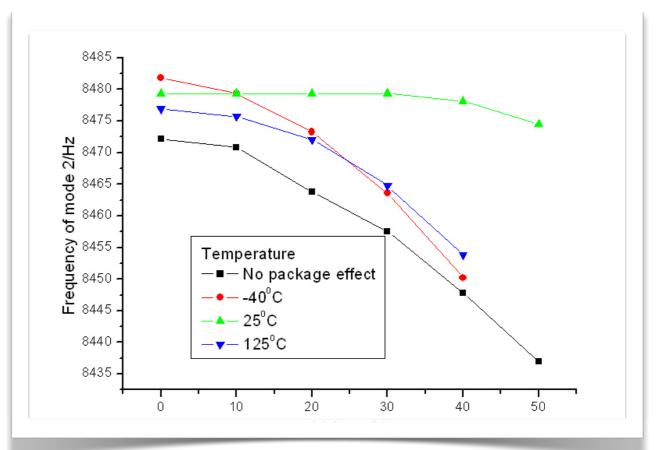

# Mode Matched Tuning Fork Gyro (M<sup>2</sup>-TFG)

# Mode Matched Tuning Fork Gyro (M<sup>2</sup>-TFG)

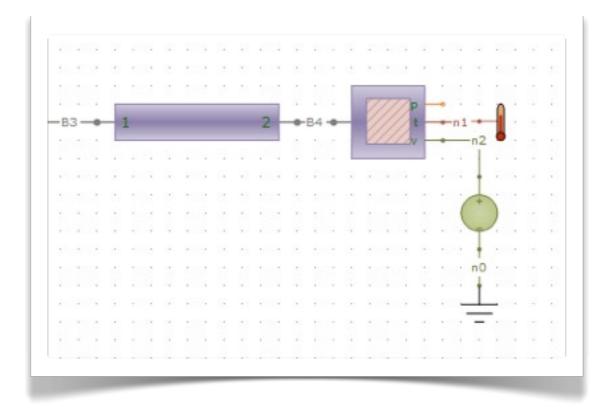

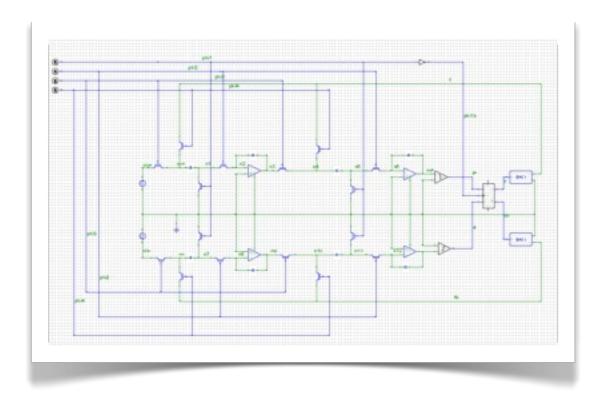

HDL Model

Cadence, Synopsys, Mentor, Mathworks

(Spectre, HSPICE, Eldo, Simulink, System Vision...)

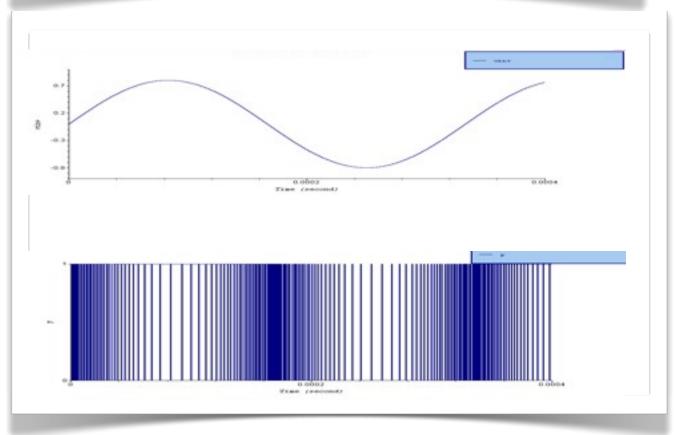

# Verilog-A modeling results...

# Summary

- New packaging approaches represent an opportunity to rethink MEMS platforms

- MEMS increasingly is subsuming the package

- MEMS Design Is a collaboration challenge

- New generation EDA tools aimed at breaking 'chain of pain'

- Allow seamless integration of WLP MEMS+ASIC